modelism功能特色

· RTL和门级优化,本地编译结构,编译仿真速度快,跨平台跨版本仿真;· 单内核VHDL和Verilog混合仿真;

· 源代码模版和助手,项目管理;

· 集成了性能分析、波形比较、代码覆盖、数据流ChaseX、虚拟对象Virtual Object、Memory窗口、Assertion窗口、源码窗口显示信号值、信号条件断点等众多调试功能;

· C和Tcl/Tk接口,C调试;

· 对SystemC的直接支持,和HDL任意混合;

· 支持SystemVerilog的设计功能;

· 对系统级描述语言的最全面支持,SystemVerilog,SystemC,PSL;

· ASIC Sign off。

· 可以单独或同时进行行为(behavioral)、RTL级、和门级(gate-level)的代码。

modelism特点

*采用直接编译结构,编译仿真速度最快*单一内核无缝地进行VHDL和Verilog混合仿真

*与机器和版本无关,便于数据移植和库维护

*与机器无关的编译代码编于保护和利用IP

*简单易用和丰富的图形用户界面,快速全面调试

*Tcl/Tk用户可定制仿真器

*完全支持VHDL/Verilog国际标准,完全支持Verilog 2001

*支持众多的ASIC和FPGA厂家库

*集成的Performance analyzer帮助分析性能瓶颈,加速仿真

*灵活的执行模式,Debug模式可以进行高效的调试,效率模式大幅度提高仿真速度

*加强的代码覆盖率功能Code coverage,能报告出statement 、branch、condition

* expression、toggle、fsm等多种覆盖率情况,进一步提高了测试的完整性

*同一波形窗口可以显示多组波形,并且能进行多种模式的波形比较(Wave Compare)

*先进的功能,可以方便地访问VHDL或者VHDL和Verilog 混合设计中的下层模块的信号,便于设计调

*支持加密IP

*集成的 C调试器,支持 用C 语言完成测试平台和模块

*支持64位的系统

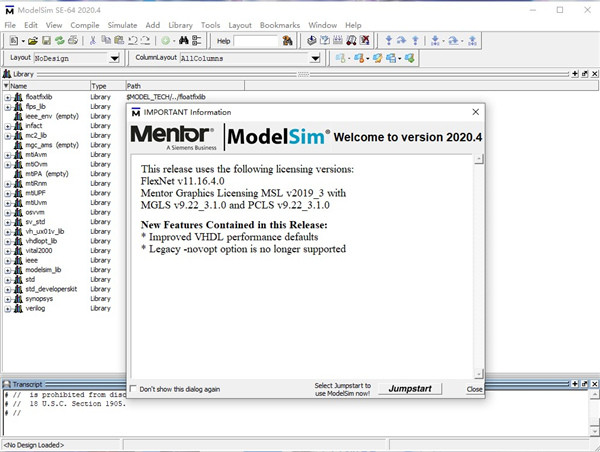

modelism使用教程

1、单击File,将鼠标移至New,选择Project...,出现如图所示的对话框。上边的红框填写你要建立的工程名称,比如我们要点亮一个led,就建立一个工程名为led的工程。下边的红框是指你要把工程建立在什么位置。其余的选项默认即可。点击ok2、接下来,点击Create new File,在弹出的对话框中填写文件名,比如led.v,add file as type,选择verilog,点击ok。因为我们要用Modelsim仿真,一般要有测试文件,再添加一个即可,和添加led.v步骤一样。我起名为tb_led.v

3、分别双击文件名,进入编辑模式。编写代码。保存后,将鼠标放在其中一个文件,右键,compile->compile all。编译通过后,会提示

# Compile of tb_led.v was successful.

# 2 compiles, 0 failed with no errors.

就可以进行仿真了

4、点击Simulate->start Simulation。记得把optimizationqian2的勾选去掉,点击work前的加号,选择测试文件,比如我写的是tb_led.v。ok。出现wave,现在把波形加进去。在 tb_led文件右键 Add->To wave ->All items in design。开始运行仿真,点击像一本书旁边带双箭头的图标。再点击放大镜可以调节波形的时间轴的坐标

共有 0条评论