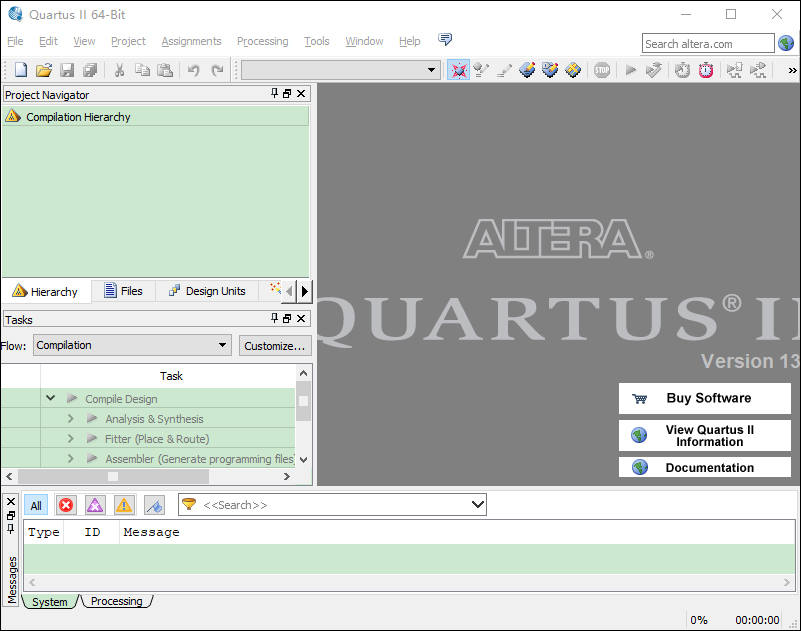

Quartus II 是 Altera 公司推出的一款强大的 FPGA/PLD 开发软件,以其高效、易用和多功能著称。它支持多种设计输入方式,包括原理图、VHDL、Verilog 和 AHDL 等,能够轻松完成从设计输入到硬件配置的全流程。特别是 Quartus II 15 版本,针对高端 Stratix V FPGA 和 SoC 设计进行了优化,编译速度提升了 25%,甚至某些项目快了三倍,极大提升了设计效率。

新版本还引入了 OpenCL SDK,为没有 FPGA 经验的软件开发人员提供了便捷的并行加速设计途径。此外,Qsys 系统集成工具对 ARM 架构的支持进一步增强,能够生成符合 AMBA 总线标准的接口,并支持 TrustZone 技术,满足安全关键系统的需求。

Quartus II 的功能非常全面,包括逻辑综合、仿真、布局布线等设计流程,还提供了 SignalTap II 等实用工具用于实时分析。软件界面友好,操作直观,适合不同层次的设计者使用。对于 FPGA 开发来说,Quartus II 几乎是必备的工具之一,尤其在处理复杂项目时,其高效的编译和强大的功能让人离不开它!

软件功能

1、OpenCL的SDK为没有FPGA设计经验的软件编程人员打开了强大的并行FPGA加速设计新世界。

从代码到硬件实现,OpenCL并行编程模型提供了最快的方法。与其他硬件体系结构相比, FPGA的软件编程人员以极低的功耗实现了很高的性能。

2、Qsys系统集成工具提供对基于ARM的Cyclone V SoC的扩展支持。

现在,Qsys可以在FPGA架构中生成业界标准AMBA AHB和APB总线接口。而且,这些接口符合ARM的TrustZone要求,支持客户在安全的关键系统资源和其他非安全系统资源之间划分整个基于SoC-FPGA的系统。

3、DSP Builder设计工具支持系统开发人员在DSP设计中高效的实现高性能定点和浮点算法。

新特性包括更多的math、h函数,提高了精度,增强了取整参数,为定点和浮点FFT提供可参数赋值的FFT模块,还有更高效的折叠功能,提高了资源共享能力。

4、效能和性能领先

对于CPLD、FPGA、SoC和HardCopy? ASIC设计,Altera Quartus? II 软件在性能和效能上是业界首屈一指的软件。通过Quartus II 软件,您无论采用哪种方法设计FPGA都会非常方便。它通过全功能高级设计工具支持复杂系统的开发,这一工具提供基于C、基于系统或者基于IP和基于模型的设计输入。Altera的高级设计流程让您的构思更迅速的在硅片中实

5、新增特性

采用Quartus II 软件v13、0,与Quartus II软件v12、1相比,编译平均快出了25%,某些设计提高了近三倍。此外,在高端领域以及优异的逻辑封装能力方面,与最相近的竞争产品相比,Quartus II软件v13、0使您的fMAX提高了23%。还有一款新产品是推出了面向OpenCL的Altera? SDK产品。

OpenCLTM和OpenCL标识是苹果有限公司的商标,使用时需要经过Khronos的授权。

6、关键新特性

编译平均快出25%

支持8内核多处理

改进适配器,实现了业界最快的硅片。

比最相近竞争产品更强的逻辑封装能力

推出面向OpenCL的Altera SDK产品

增强Qsys系统集成工具,包括:

支持ARM? TrustZone?技术,以及高级外设总线(APBTM)和高性能总线(AHBTM)。

支持VHDL总线功能模型(BFM)

收发器工具包增强功能,包括:

面向Stratix? V FPGA的误码检查

能够测量并报告每一工作收发器通道的数据速率

SignalTap? II逻辑分析器增强功能,包括:

不需要重新编译,能够改变基本触发工作。

来自Altera SoC硬核处理器系统(HPS)事件的交叉触发

为大部分28 nm器件提供编程器目标文件(POF)支持

简化了更新IP内核过程

采用新安装程序,简化了软件和器件系列安装。

7、器件支持

Stratix V:FPGA 除5SGSD6和5SGSD8之外的所有产品器件的最终时序模型,除Stratix V GT器件之外的所有产品器件功耗模型,为判决反馈均衡提供MegaWizard?支持

Arria V:FPGA 5AGXA5 (190K逻辑单元)、5AGXA7和5AGTC7 (242K逻辑单元)器件的POF支持,5AGXB1、5AGXB3和5AGTD3的最终时序模型,所有Arria? V GZ器件的最终时序模型

Cyclone V:FPGA 5CGXC4、5CGXC5, 5CGXC7(M484)、5CGTD5和5CGTD7(M484)器件的POF支持

Cyclone V:SoC 5CSXC6ES和5CSEA6ES (110K逻辑单元)器件的POF支持,后适配VHDL功能仿真支持

软件特色

1、可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;

2、芯片(电路)平面布局连线编辑;

3、LogicLock增量设计方法,用户可建立并优化系统,然后添加对原始系统的性能影响较小或无影响的后续模块;

4、功能强大的逻辑综合工具;

5、完备的电路功能仿真与时序逻辑仿真工具;

6、定时/时序分析与关键路径延时分析;

7、可使用SignalTap II逻辑分析工具进行嵌入式的逻辑分析;

8、支持软件源文件的添加和创建,并将它们链接起来生成编程文件;

9、使用组合编译方式可一次完成整体设计流程;

10、自动定位编译错误;

11、高效的期间编程与验证工具;

12、可读入标准的EDIF网表文件、VHDL网表文件和Verilog网表文件;

13、能生成第三方EDA软件使用的VHDL网表文件和Verilog网表文件。

软件亮点

【设计流程】

quartus ii 提供了完整的FPGA设计流程,包括设计输入、仿真、综合、布局布线、下载等步骤。

【设计输入】

支持多种硬件描述语言,如Verilog和VHDL,同时也支持原理图设计。

【仿真】

内置的仿真工具可以帮助用户在硬件实现前对设计进行测试。

【项目组织】

提供项目浏览器,方便用户管理项目文件和组织设计。

共有 0条评论